Demands on System from Explicit/Implicit Analysis

- Explicit

- -Quick Communication between processors

- -Good FPU

- Implicit

- -Low memory latency

- -High memory bandwidth

#### AMD Opteron<sup>™</sup> delivers:

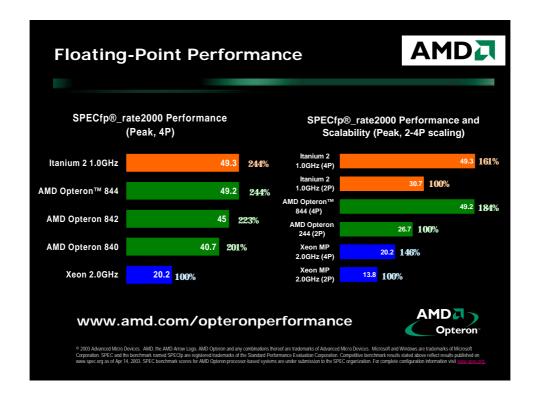

- 1. Breakthrough 64-bit performance

- 2. Complete 32-bit compatibility

- 3. Industry leading price/performance

22 May 2003 LS-DYNA Users Conference 2003

# Benefits of AMD Opteron<sup>™</sup> for LS-DYNA

- Performance

- -Raw Performance

- -Price Performance

- Scalability

- -On-Chip Cache

- –HyperTransport™

- Low Memory Latency

- Memory Addressability

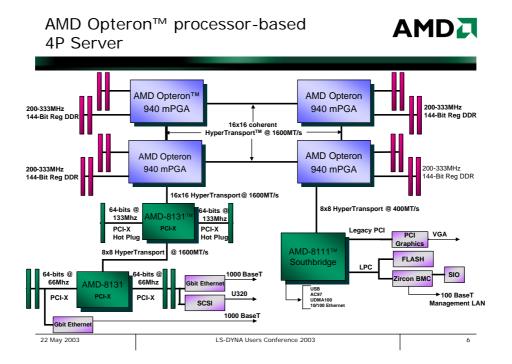

4P, 32GB AMD Opteron™ Processor-based System

22 May 2003

LS-DYNA Users Conference 2003

3

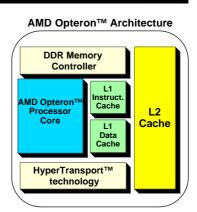

# AMD Opteron™ SOC Architecture Overview

- First AMD64 processor

- Aggressive out-of-order, 9-issue superscalar processor

- Integrated DDR memory controller

- Leading performance in integer, floating point and multimedia

- -AMD64, x87, MMX<sup>™</sup>, 3DNow!<sup>™</sup>, SSE, SSE2

- Glueless multiprocessing through HyperTransport™

- Expandable IO through HyperTransport

22 May 2003

LS-DYNA Users Conference 2003

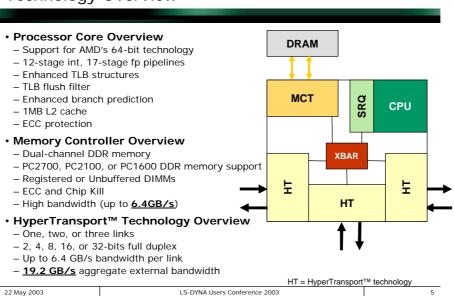

# AMD Opteron™ Processor Technology Overview

### The Rewards of Good Plumbing

#### High Bandwidth

- -2P system is designed to achieve 7 GB/s aggregate memory Read bandwidth

- -4P system is designed to achieve 10 GB/s aggregate memory Read bandwidth

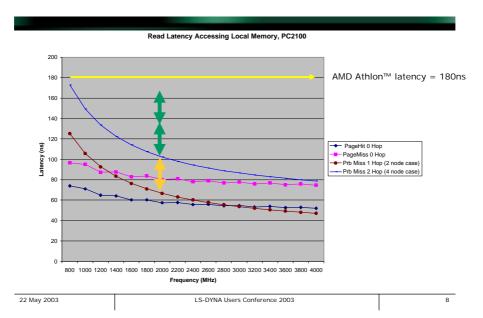

#### Low Latency

- -Average 2P unloaded latency (page hit) is designed to be < 120 ns

- -Average 4P unloaded latency (page hit) is designed to be < 140 ns

- -Latency under load increases slowly due to excess Interconnect Bandwidth

- -Latency shrinks quickly with increasing CPU clock speed and HyperTransport™ link speed

22 May 2003 LS-DYNA Users Conference 2003 7

## **Integrated Memory Controller**

Latency (Local Memory Access, Registered Memory, CAS2)

The Result

AMD Opteron<sup>™</sup> delivers:

- 1. Breakthrough 64-bit performance

- 2. Complete 32-bit compatibility

- 3. Industry leading price/performance

22 May 2003 LS-DYNA Users Conference 2003 10

# **Cautionary Statement**

Trademark Attribution

•This presentation contains forward-looking statements, which are made pursuant to the safe harbor provisions of the U.S. Private Securities Litigation Reform Act of 1995. Forward-looking statements are generally preceded by words such as "expects," "plans," "believes," "anticipates," or "intends." Investors are cautioned that all forward-looking statements in this presentation involve risks and uncertainties that could cause actual results to differ materially from current expectations. Forward-looking statements in this presentation involve the risks that AMD Opteron™ processors will not perform pursuant to their design specifications, will not achieve customer and/or market acceptance, and that third-party solution vendors will not provide the infrastructure necessary to support these products. We urge investors to review in detail the risks and uncertainties in the company's U.S. Securities and Exchange Commission filings, including the most recently filed Form 10-K.

•AMD, the AMD Arrow logo, AMD Opteron, AMD Athlon, and combinations thereof, AMD-8111 and AMD-8131 are trademarks of Advanced Micro Devices, Inc. HyperTransport is a licensed trademark of the HyperTransport Technology Consortium. Other product and company names used in this publication are for identification purposes only and may be trademarks of their respective companies.

| 22 May 2003 | LS-DYNA Users Conference 2003 | 11 |

|-------------|-------------------------------|----|